前几天英特尔CEO在接受采访时表示自家的制程工艺虽然现在不如友商,但是未来就会成为遥遥领先的工艺,起码领先友商尤其是台积电2年。这让台积电这样的晶圆代工厂商十分地不满,表示英特尔这是在吹牛,通过内部评估,台积电的制程工艺要比英特尔更强。当然在IEDM 2023国际电子元件会议上,台积电自己也公布了最新的路线图,称将会在2023年实现1nm制程的量产,从而满足一块封装芯片内实现1万亿个晶体管的壮举。

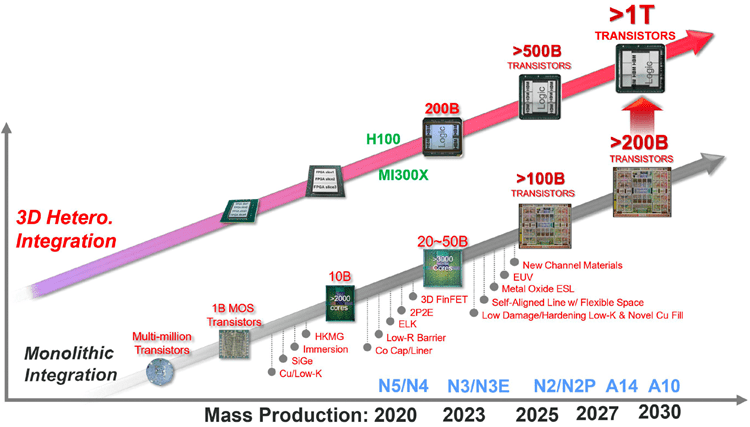

目前台积电的最新工艺为N3也就是3nm,已经应用在A17处理器上,主要是增加了能耗比,而到了2025年至2027年,工艺制程就准备冲击N2也就是2nm,而这也是台积电与英特尔大打口水仗的制程,单芯片能够达到1000亿个晶体管,而整个芯片的封装最高可以达到5000亿个晶体管,已经远超现在的芯片。为了实现如此强大的制程,台积电将会采用EUV极紫外光刻、新材料、金属氧化物ESL等工艺,以及更加先进的封装技术。随后台积电开始学习英特尔的命名方法,将制程工艺命名为A14、A10,应该这里的A就是埃的意思,也就是0.1nm。

从台积电给出的路线图来看,终极工艺应该是A10也就是1nm工艺,在这个工艺上,台积电希望能够达成单核心2000亿个晶体管的壮举,而整个封装芯片更是可以达到1万亿个晶体管。目前半导体领域中,英伟达的计算卡H100拥有单芯片800亿个晶体管,也就是说A10工艺能够实现的晶体管数量是H100的12.5倍,而多芯片则是AMD的MI300X,拥有1350亿个晶体管,A10工艺的晶体管数量是其7.4倍。

而从目前给出的路线图来看,能够和台积电竞争的似乎只有英特尔,之前英特尔也表示将会在2030年实现一万亿个晶体管的壮举,似乎这两家是针锋相对。不过作为目前最为尖端的半导体工艺,制程的跳票并不是什么罕见的事情,加上制造成本的快速提升,届时如果能在2023年看到A14工艺,估计就谢天谢地了。